30分以内の回答、1時間のエンジニアリング応答、24時間のテクニカルサポートを提供することで、お客様の待ち時間を短縮し、あらゆる面から製品開発と生産サイクルを短縮し、市場投入までの時間を短縮し、製品の市場占有を迅速に行います。

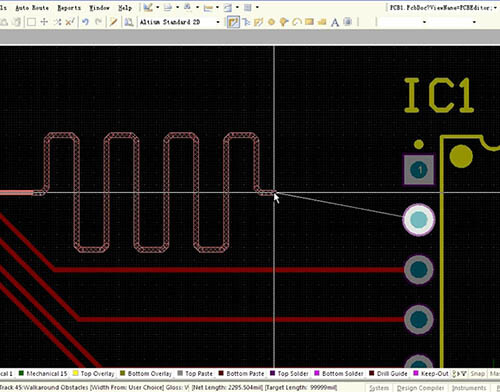

10年以上の発展で、我々は年々大きくなり、技術と能力を増やし続けている。一般的な基板から無線周波数PCB基板、マイクロ波基板、多層基板、FPCB PCB、HDI PCB、多層基板、IC基板、ICテスト基板。

私たちはお客様とウィンウィンのビジネスを探していて、私達の会社の文化の中で小さいお客様も大きいお客様もなくて、常に最高の努力を尽くして良いサービスを提供するのが私達の目標です。

材料の幅広い選択、ブランド材料のサプライヤー、例えば: Isola、Panasonic、TUC、ITEQ、盛益、KB、Rogers、Arlon、Taconic在庫材料: FR408,370HR,TU872,RO4350b,RO4003c,RT5880,RO3010,RO3003,RT35,TLY5,Megtron4,Megtron6,S1000-2,IT180,F4BMカスタムプリント基板。

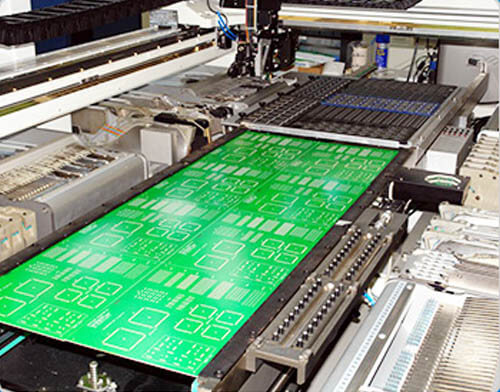

FR-4 PCB、多層基板、HDI PCB、セラミック基板、PTFE PCB、ミックス基板、炭化水素PCB、テフロン基板、無線周波数プリント基板、ロジャース基板、Taconic PCBに対応している。先進的なPCB ERP追跡管理システムの納期は業界をリードし、PCBの時間通りの配達率で95%以上です。

厳格な品質管理システムは私達が中国で最も経験のあるプリント基板PCBメーカーの一つであることを保証して、10年以上の経験を持っています。iPcbプロのPCBプロトタイプを製造するPCB工場、IPC Class III標准は顧客の要求に応じて選択することができます。

2021-04-21

2020-11-09

2021-07-22