電子工学的ピラミッドに集積回路パッケージの位置は、ピラミッドの頂点であり、ピラミッドの土台でもある。両方の位置に同時にいるというのには十分な根拠がある。トランジスタなどの電子部品の密度という観点から言えば、ICはエレクトロニクスの先端を表している。しかし、ICはまた出発点であり、基本的な構造単位であり、私たちの生活の中でほとんどの電子システムを構成する基礎である。同様に、ICはモノリシックチップや基本電子構造だけでなく、ICの種類は千差万別(アナログ回路、デジタル回路、無線周波回路、センサなど)であるため、パッケージに対する需要と要求もそれぞれ異なる。

集積回路パッケージはまた、電子機器全体の需要と発展に十分に適応しなければならない。各種類の電子機器、計器の機能が異なるため、その全体構造と組立要求も異なることが多い。そのため、集積回路パッケージは、様々な整機の必要性を満たすためには、多種多様でなければならない。

集積回路パッケージは集積回路の発展に伴って前進する。航空宇宙、航空、機械、軽工業、化学工業などの各業界の発展に伴い、機械全体も多機能、小型化の方向に変化している。これにより、集積回路の集積度が高くなり、機能が複雑になる必要があります。そのため、集積回路のパッケージ密度はますます大きくなり、リード線数はますます多くなり、体積はますます小さくなり、重量はますます軽くなり、モデルチェンジはますます速くなり、パッケージ構造の合理性と科学性は集積回路の品質に直接影響を与えることが求められている。

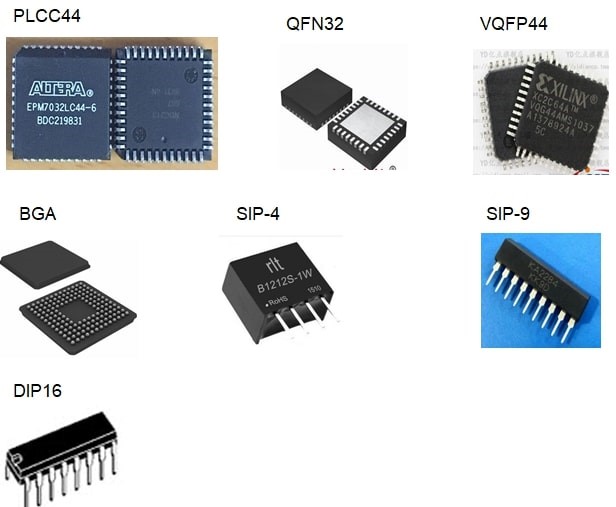

集積回路パッケージのタイプ

パッケージ材料によって区分され、金属パッケージ、セラミックパッケージ、プラスチックパッケージに分けることができる。

金属パッケージは主に軍需産業や宇宙技術に用いられ、商業化された製品はない。

セラミックパッケージは金属パッケージより優れており、軍事製品にも使用されており、少量の商業化市場を占めている。

プラスチックパッケージは、低コストで、プロセスが簡単で、信頼性が高く、市場シェアのほとんどを占めているため、消費電子に使用されています。

PCBボードとの接続方法によって、次のように区分されます。

TH−Pin Through Hole、スルーホール式。

SMT-SurfaceマウントTechnology、表面貼付式。

現在、市場ではほとんどのICがSMT式に採用されている。

集積回路パッケージ外形によって、SOT、QFN、SOIC、TSSOP、QFP、BGA、WLCSPなど、パッケージ形式とプロセスは段階的に高度で複雑になっています。パッケージ形式を決定する2つの重要な要素:パッケージ効率、チップ面積/パッケージ面積、できるだけ1:1に近い、ピンの数。ピンの数が多ければ多いほど、高級になりますが、プロセスの難易度も高くなります。その中で、wafer levelパッケージはFlip Chip技術とベアチップパッケージを採用したため、チップ面積/パッケージ面積=1:1に達し、現在の高級技術である。

パッケージ(Package)はチップにとって必要であり、極めて重要である。パッケージとは、チップの保護や熱伝導性の向上だけでなく、チップ内部と外部回路の橋渡しや仕様共通機能をコミュニケーションするための半導体集積回路チップを実装するためのハウジングのことでもある。

パッケージの主な役割は次のとおりです。

(1)物理的保護。

チップは空気中の不純物によるチップ回路の腐食による電気性能の低下を防止し、チップ表面及び接続リード線などを保護し、かなり柔らかいチップを電気又は熱物理などの面で外力損害及び外部環境の影響から保護しなければならないため、同時にパッケージ化によってチップの熱膨張係数とフレームや基板の熱膨張係数をマッチングさせることで、熱などの外部環境の変化による応力やチップ発熱による応力を緩和することができ、チップ破損の故障を防止することができる。

放熱の要求に基づいて、パッケージは薄いほど良く、チップの消費電力が2 Wより大きい場合、パッケージには放熱フィンまたはヒートシンクを追加して、その放熱冷却機能を強化する必要がある、5~1 OWの場合は強制冷却手段を取らなければならない。一方、パッケージ化されたチップは、実装や輸送にも便利です。

(2)電気的接続。

集積回路パッケージの寸法調整(ピッチ変換)機能は、チップの細いリードピッチから実装基板の寸法ピッチに調整することができ、実装作業を容易にすることができる。例えばサブミクロン(現在は0.1μm以下に達している)を特徴寸法とするチップから、10μm単位のチップボンディングスポット、さらに100μm単位の外部ピン、リアソードのミリ単位のプリント配線板まで、すべてメートルをカプセル化することによって実現されている。

パッケージはここで小さいものから大きいものへ、難しいものから簡単なものへ、複雑なものから簡単なものへと変換する役割を果たしており、それによって操作費用と材料費用を低減することができ、しかも作業効率と信頼性を高めることができ、特に配線長とインピーダンスの配位子を実現することによって接続抵抗、寄生容量とインダクタンスをできるだけ低減することによって正しい信号波形と伝送速度を保証することができる。

(3)標準規格化。

規格共通機能とは、パッケージの寸法、形状、ピン数、ピッチ、長さなどに標準規格があり、加工が容易であるとともに、プリント基板との組み合わせも容易であり、関連する生産ライン及び生産設備はすべて汎用性を持っている。これはパッケージユーザー、回路基板メーカー、半導体メーカーにとって便利で、標準化にも便利です。

対照的に、ベアチップの実装とフリップアップには現在、この点での優位性はない。組立技術の良し悪しはチップ自体の性能の発揮とそれに接続されたプリント配線基板(PCB)の設計と製造にも直接影響するため、多くの集積回路製品にとって、組立技術は非常に重要な一環である。

先進的な集積回路パッケージ技術は半導体業界にとって極めて重要であり、それは3次元スタックと異種集積を通じてチップ集積度とシステム性能を高め、小型化を実現し、消費電力を下げ、コストを減らし、新材料と新技術の革新を推進し、そして国際競争における半導体製品の技術力と信頼性を強化した。